# ACS APPLIED MATERIALS & INTERFACES

# Deep Etching of Single- and Polycrystalline Silicon with High Speed, High Aspect Ratio, High Uniformity, and 3D Complexity by Electric Bias-Attenuated Metal-Assisted Chemical Etching (EMaCE)

Liyi Li,<sup>†</sup> Xueying Zhao,<sup>†</sup> and Ching-Ping Wong<sup>\*,†,‡</sup>

<sup>†</sup>School of Materials Science and Engineering, Georgia Institute of Technology. 771 Ferst Drive, Atlanta, Georgia 30332, United States

<sup>‡</sup>Department of Electronic Engineering, The Chinese University of Hong Kong, Shatin, Hong Kong

Supporting Information

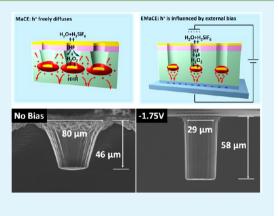

**ABSTRACT:** In this work, a novel wet silicon (Si) etching method, electric bias-attenuated metal-assisted chemical etching (EMaCE), is demonstrated to be readily available for three-dimensional (3D) electronic integration, microelectromechinal systems, and a broad range of 3D electronic components with low cost. On the basis of the traditional metal-assisted chemical etching process, an electric bias was applied to the Si substrate in EMaCE. The 3D geometry of the etching profile was effectively controlled by the bias in a real-time manner. The reported method successfully fabricated an array of over 10 000 vertical holes with diameters of 28  $\mu$ m on 1 cm<sup>2</sup> silicon chips at a rate of up to 11  $\mu$ m/min. The sidewall roughness was kept below 50 nm, and a high aspect ratio of over 10:1 was achieved. The 3D geometry could be attenuated by the variable applied bias in real time. Vertical deep etching was realized on (100)-, (111)-Si, and polycrystalline Si substrates. Complex features with lateral dimensions of 0.8–500  $\mu$ m were also fabricated with submicron accuracy.

**KEYWORDS:** wet etching, electrical bias, 3D microstructures

# INTRODUCTION

Fabrication of three-dimensional (3D) microstructures on elemental silicon (Si) is a fundamental process in manufacturing of a broad range of components in modern microelectronic devices, such as through silicon vias,<sup>1</sup> microelectromechanical systems,<sup>2</sup> optoelectronic devices<sup>3</sup> and etc.<sup>4,5</sup> Compared to the components that spread on the two-dimensional (2D) surface of Si, the 3D components utilized the volume inside Si substrates, thus gained much higher integration density and unique functions. Currently, the 3D components are majorly fabricated by bulk micromachining of Si (BMS), where a certain volume of Si inside the wafers or chips was selectively removed by wet solution (wet etching) or plasma (dry etching). However, both methods have significant limitations. Wet etching generally possesses the nature of cost efficiency, but the shape of the etching profiles is limited because the etching direction depends on the crystalline orientation of the substrate. Dry etching is virtually capable of etching micro-structures with arbitrary geometry.<sup>6,7</sup> However, its application in large-scale manufacturing has been hindered by expensive instrumentation and maintenance. In this work, we present a novel wet BMS technology that successfully fabricated vertical holes and trenches with high aspect ratio, high uniformity, high speed, high pattern density, submicron precision, 3D geometric complexity, and low cost.

It has long been known that Si can be etched in hydrofluoric acid (HF) solution with the presence of electronic holes  $(h^+)$ :

$$Si + 6HF + 4h^+ \rightarrow SiF_6^{2-} + 6H^+$$

(1)

Holes (h<sup>+</sup>) can be either generated by reduction of oxidative chemicals (for example, HNO<sub>3</sub>) or injected from external electric power supply, as in the cases in isotropic wet etching<sup>8</sup> or electrochemical etching,<sup>9,10</sup> respectively. Because the etching of Si by pure HF is extremely slow,<sup>11</sup> selective etching of Si in a HF-h<sup>+</sup> system can be realized by controlling the distribution of h<sup>+</sup> concentration inside the Si substrate. Recently, a novel HF-based etching method, metal-assisted chemical etching (MaCE), has received extensive attention.<sup>12–17</sup> In MaCE, noble metal with defined shape and position is deposited on the top surface of Si. MaCE occurs when the metal-loaded Si is immersed in a HF–hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) solution; h<sup>+</sup> is generated by reduction of hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) under the catalysis of noble metals:

$$H_2O_2 + 2H^+ \xrightarrow{\text{noble metal}} 2H_2O + 2h^+$$

(2)

Received:June 23, 2014Accepted:September 2, 2014Published:September 4, 2014

16782

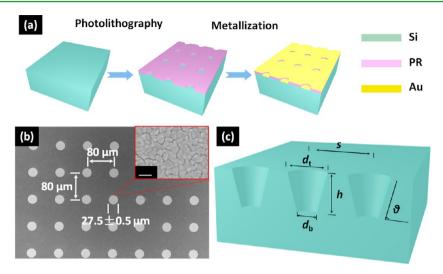

**Figure 1.** (a) Schematics of processing flow. The blocks in green, purple, and gold refer to Si substrate (Si), photoresist (PR), and Au catalysts (Au), respectively. (b) Top-view SEM image of Au patterns on silicon after lift-off of PR; (inset) morphology of Au pattern surface under high magnification (scale bar = 100 nm). (c) Schematic etching profile after MaCE and parameters used for describing the etching profile.

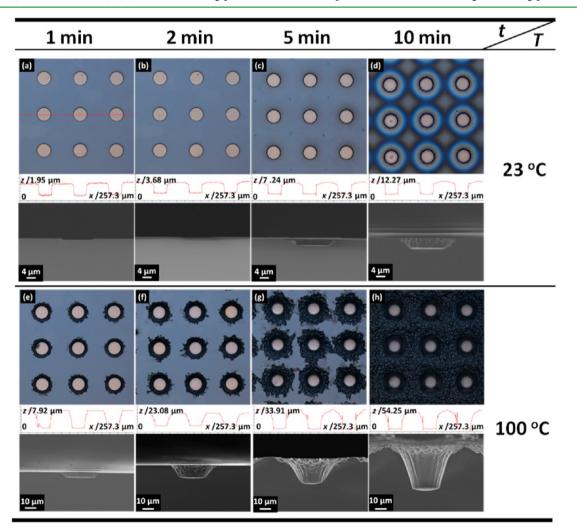

Figure 2. Etching profiles of 28  $\mu$ m Au–Si(100) in  $\rho$ (0.37)<sup>1.8</sup> for (a) 1, (b) 2, (c) 5, and (d) 10 min at 23 °C and for (e) 1, (f) 2, (g) 5, and (h) 10 min at 100 °C. (Top) Top-view OCM images, (middle) optical cross sections, (bottom) and SEM cross sections are shown in each set of figures.

Then,  $h^+$  induces the etching of Si adjacent to the metal catalysts following eq 1. The geometry of the etching profile can be controlled by the catalysts and etchant. Uniform silicon

nanowires have been successfully fabricated by MaCE using mesh-shaped metal film.<sup>18-21</sup> However, BMS has been challenging for MaCE.<sup>22</sup> Recently, our group identified the

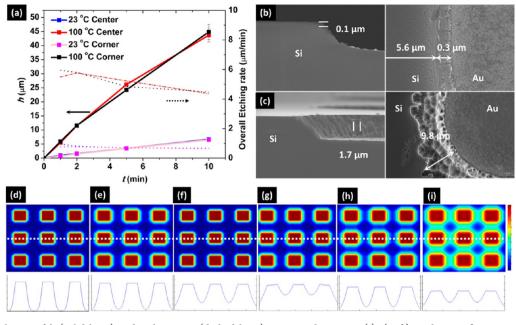

**Figure 3.** (a) Evolution of *h* (solid lines) and etching rate (dashed lines) versus etching time (*t*). (Left) High-magnification cross-sectional and (right) top-view SEM images of Au–Si boundary area after 1 min of etching at (b) 23 °C and (c) 100 °C. (d–i, top) Simulated 2D distribution of  $c(h^+)$  in arbitrary unit (a.u.) corresponding to experiments shown in Figure 2a–f, respectively. The color bar indicates the relative value of  $c(h^+)$  in the 2D plots with nominal dimension of 200 × 200  $\mu$ m. (d–i, bottom) Corresponding distribution of c(h+) in a.u. along the dashed line.

transport of HF and h<sup>+</sup> to be the two critical processes for uniform MaCE. On the basis of this understanding, we established the uniform MaCE condition, in which a HF– H<sub>2</sub>O<sub>2</sub> solution with a low HF-to-H<sub>2</sub>O<sub>2</sub> concentration ratio ( $\rho$ ) was used as the etchant to enable an electropolishing-favored h<sup>+</sup> transport; a nanoporous gold (Au) thin film was used as the catalyst to enable a through-catalyst transport of HF. A single uniform 2  $\mu$ m wide trench was successfully fabricated under the uniform etching condition.<sup>23</sup> In this work, we investigate the MaCE of multiples microstructures with a broader range of shape and dimensions.

In the context mentioned above, we fabricated an array of circular Au catalysts with diameters of 27.5  $\pm$  0.5  $\mu$ m, spacing (the distance between the centers of two adjacent patterns) of 80  $\mu$ m, and nominal thickness of 15 nm on (100)-oriented Boron-doped (resistivity, 1–10  $\Omega$ ·cm) single crystalline Si wafers by photolithography and electron-beam evaporation (Figure 1a, referred to as the "28  $\mu$ m Au–Si(100)" sample). Nanopores could be observed within the catalysts using a scanning electron microscope (SEM) (Figure 1b). The sample was cut into  $1 \text{ cm}^2$  chips (referred to as the "chip" hereafter) for MaCE tests. The number of Au patterns on one chip is estimated to be 10<sup>4</sup>. One drop (ca. 0.2 mL) of  $\rho(0.22)^{0.9}$  HF-H2O2 aqueous solution was slowly dropped on the whole surface of 28  $\mu$ m Au-Si(100) chip and kept for 1 min before the chip was fully immersed in 32 mL  $\rho(0.37)^{1.8}$  HF-H<sub>2</sub>O<sub>2</sub> aqueous solution (used in all following experiments unless specified). The name of the  $HF-H_2O_2$  etchant is formatted as  $\rho(x)^{y}$  to shows its composition, where  $x = [HF]/([H_2O_2] +$ [HF]) and y = [HF] ([HF] is the concentration of HF in moles per liter). The chip was etched with the photoresist on the top surface. Geometric parameters of the etching profile are defined in Figure 1c, including top diameter  $(d_t)$ , bottom diameter  $(d_b)$ , sidewall angle ( $\theta$ ), maximum etching depth (h) and spacing (s). After pre-etching by the  $\rho(0.22)^{0.9}$  droplet, Au catalysts moved uniformly into Si substrate (Figure S2a, Supporting Information, while Si surrounding Au was also etched by with a width of 232 nm (Figure S2b, Supporting Information). Small etched pits were found right beneath the nanopores, both near the Au-Si boundary and under the center of Au patterns (Figure S2c,d, Supporting Information), indicating that HF was able to transport through the nanoporous Au catalysts. Also, we found the pre-etching step in the  $\rho(0.22)^{0.9}$  etchant helped improve the reproducibility of experiments. The lower  $\rho$  value of preetching solution was found to facilitate a more stable etching at the initial stage. In a control experiment in which the chip was directly immersed in bulk  $\rho(0.37)^{1.8}$  etchant without the preetching, some Au patterns were lifted off from Si substrate before any etching occurred. The pre-etching process is conducted in all the following experiments, and the time of pre-etching is excluded from the etching time mentioned below.

After immersion in the bulk  $\rho(0.37)^{1.8}$  etchant, Au moved deeper into the Si chips. We studied the MaCE of 28  $\mu$ m Au-Si(100) chips for 1 min, 2 min, 5 and 10 min at 23 and 100 °C. The etching profiles in each test are revealed by optical confocal microscopy (OCM) (top and middle images) and SEM (bottom images) in Figure 2. In the OCM images, Au and the Si between Au are shown in gold and blue. After etching, the catalysts moved vertically into the Si substrate and kept flat. The etching depth (h) and etching rate of each test are summarized in Figure 3a. The original data for plotting Figure 3a can be found in Tables S1 and S2 (Supporting Information). Etching depth (h) was measured from OCM cross sections of 9 adjacent etched holes in both center part (averaged to give  $h_{\text{center}}$ ) and corner part (averaged to give  $h_{\text{corner}}$ ) of the 1 cm<sup>2</sup> chips. The etching rate is calculated by dividing h by the corresponding etching time. After 10 min of MaCE,  $h_{center}$ reached 6.7  $\pm$  0.1  $\mu$ m at 23 °C and 43.7  $\pm$  2.5  $\mu$ m at 100 °C, while  $h_{\rm corner}$  was 6.5  $\pm$  0.2  $\mu {\rm m}$  at 23  $^{\circ}{\rm C}$  and 44.9  $\pm$  2.7  $\mu {\rm m}$  at 100 °C. Across the 10 min, the etching rate ranges were 0.95-0.67  $\mu$ m/min at 23 °C and 5.50–4.37  $\mu$ m/min at 100 °C. The

uniformity and speed of etching along the vertical direction at 100  $^{\circ}$ C is comparable to the commercial dry etching method.<sup>24</sup> The slight decrease of etching rate versus etching time may be due to the increasing difficulty of mass transport inside the etched holes.

In the above MaCE experiments, besides the vertical etching, significant etching also occurred in nonvertical directions. After 10 min of MaCE, the top surface of Si between Au patterns turned colorful at 23 °C (Figure 2d) and became completely black at 100 °C (Figure 2h), as can be observed in OCM images. Under magnified SEM images, these regions show a porous morphology. Actually, formation of the porous regions started from the first 1 min of MaCE, when the Si near Au-Si boundary was found completely removed by 300 nm in width (completely removed region, CRR) at 23 °C, and a porous layer expanded with a width of 5.6  $\mu$ m beyond the CRR (Figure 3b); at 100 °C, the surface of CRR was decorated with much larger pores and extended 9.8  $\mu$ m out of Au-Si boundary (Figure 3c). Apparently, the porous region and CRR are detrimental to electronic components, and thus, it is imperative to suppress the excessive etching before MaCE can be applied to any component fabrication.

Given that the etching of bare silicon by  $H_2O_2$ -HF solution is negligible,<sup>25</sup> we attribute the appearance of these regions to the electrochemical etching process (eq 1) induced by excessive h<sup>+</sup>. In  $\rho(0.37)^{1.8}$  etchant where  $c(H_2O_2)$  is high, the amount of h<sup>+</sup> generated in eq 2 exceeds the amount that can be consumed by the etching of Si underneath the Au catalysts (i.e., the vertical etching). The excessive h<sup>+</sup> tends to diffuse to the sidewall and top surface of Si, which induces the nonvertical excessive etching in these regions (Figure 4a). Because both the vertical etching and the excessive etching follow the same process in eq 1, they both become faster at elevated temperature.<sup>26</sup> To further illustrate the origin of excessive etching, we simulated the distribution of accumulated h<sup>+</sup> concentration  $(c(h^+))$  by a 2D constant source model.<sup>23,27</sup> The details of simulation can be found in the Supporting Information. Figure 3d-i shows the distribution of  $c(h^+)$ plotted in 2D planes that contains 9 Au patterns (top images) and along 1D lines that intersect with 3 Au patterns (bottom images). Au patterns are set as the constant source of h<sup>+</sup>. As visualized in both images, a significant amount of h<sup>+</sup> diffuses to the Si between Au  $(c(h^+)_{Si})$  relative to that under the Au patterns  $(c(h^+)_{Au})$  as the etching proceeds. At 23 °C,  $c(h^+)_{Si}$ reaches ca. 60% of  $c(h^+)_{Au}$  after 10 min; at 100 °C,  $c(h^+)_{Si}$ reaches ca. 45% of  $c(h^+)_{Au}$  only after 2 min. The evolution of  $c(h^+)_{Si}$  in both cases is consistent with the expansion of porous region and CCR, which supports our assumption that excessive etching is induced by excessive h<sup>+</sup>.

In this work, we demonstrate that the excessive etching can be controlled by using an external electric bias during MaCE process. We name the novel etching method as electric biasattenuated MaCE (EMaCE). To maintain the high etching rate, all following experiments are done at 100 °C. On the basis of the above discussion, the excessive etching is supposed to originate from the excessive  $h^+$ . If a negative bias is applied from the back side of the chips, excessive  $h^+$  will be drawn away from the sidewall and top surface to the back side of Si by electrostatic force, and the extent of excessive etching can be controlled by the strength of the bias (Figure 4b). The idea was realized by connecting the chip to the negative output terminal of a direct current electric power supply. To ensure good electrical contact between the chip and power supply, we

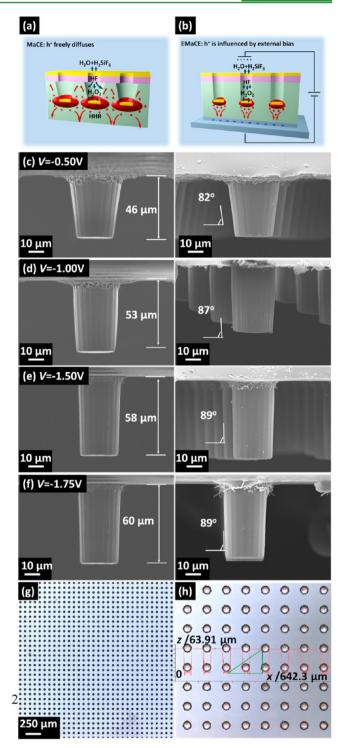

**Figure 4.** Schematics of charge transport in (a) MaCE and (b) EMaCE. Cross-sectional SEM images of the (left) chips and (right) polymer replica after EMaCE at (c) -0.50, (d) -1.00, (e) -1.50, and (f) -1.75 V for 10 min. (g) OCM image and (h) cross section of the etched chip in panel f.

mounted the chip on a gallium-wet copper foil that was wired to the power supply. The chip and copper foil were further packaged in a homemade carrier in which all surfaces were covered by polymer except the front surface of the chip (Figure S3, Supporting Information). The chip-copper-carrier assembly is referred as the working electrode. Meanwhile, a platinum (Pt) wire was connected to the positive terminal as

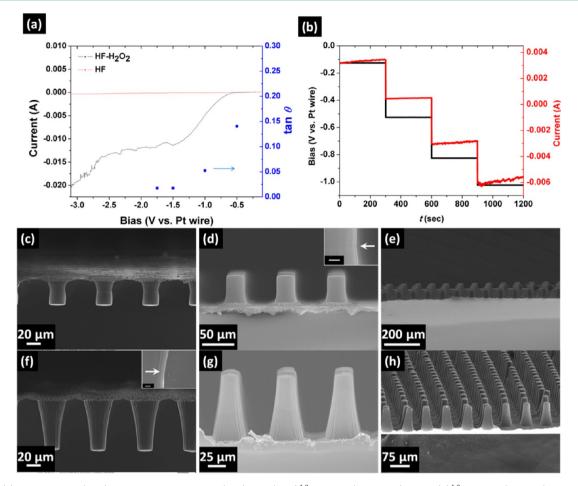

**Figure 5.** (a) Current-bias (I-V) curve of 28  $\mu$ m Au-Si(100) in  $\rho(0.37)^{1.8}$  etchant (black line) and  $\rho(1)^{1.8}$  etchant (red line) in a continuous EMaCE experiment; *h* and  $\theta$  of the etching results shown in Figure 4 c-f are also plotted. (b) Evolution of applied bias and measured current versus etching time in a stepwise EMaCE experiment. Cross-sectional SEM of (c) chips and (d and e) polymer replica etched under the conditions of the black line in panel a. Cross-sectional SEM of (f) chips and (g and h) polymer replica etched under the conditions of panel b.

the counter electrode. In EMaCE, both electrodes were immersed in the HF-H2O2 etchant, while a certain value of voltage (V) was set in the power supply so that the chip was negatively biased by V relative to the Pt wire (referred as "at  $-V^{"}$ ). The details of experimental setup and carrier fabrication are described in the Supporting Information. The first 30 s is included in the etching time mentioned below. After the 30 s of etching at no bias,  $d_t$  slightly increased to 29  $\mu$ m. After EMaCE, we used polymer replica to reveal the true 3D geometry of the etching profile (see explanation in Figure S4, Supporting Information). The cross sections of the etched chips and corresponding polymer replica after EMaCE at -0.5, -1.0, -1.5, and -1.75 V for 10 min are shown in Figure 4c-f, respectively. Both cross sections consistently show a decrease of  $\theta$  and an increase of *h* as the bias becomes more negative (referred to as an increase of bias). The results support our proposed mechanism that diffusion of excessive h<sup>+</sup> can be influenced by negative bias; as the strength of bias increases, more h<sup>+</sup> that tends to diffuse toward the top surface and sidewalls is driven toward the backside. In other words, the negative bias redistributes the  $c(h^+)$  in 3D space so that excessive etching is suppressed and the vertical etching is enhanced. When the bias was increased to -1.75 V, the surface of Si between Au patterns keeps its original color and polished morphology (Figure 4g), and  $d_t$  remains 29  $\mu$ m, indicating a complete suppression of excessive etching. Figure 4h shows the

top-view OCM images and cross sections of the chip etched at -1.75 V. The  $h_{\text{center}}$  and  $h_{\text{corner}}$  are measured to be  $59.8 \pm 0.5$   $\mu$ m and  $60.5 \pm 0.5 \ \mu$ m, respectively. However, a much larger discrepancy was discovered between  $h_{\text{center}}$  and  $h_{\text{corner}}$  in EMaCE at -1.0 and -1.50 V (Figure S5, Supporting Information). The smaller discrepancy of  $h_{\text{center}}$  and  $h_{\text{corner}}$  found at -1.75 V is probably due to a complete suppression of excessive h<sup>+</sup> diffusion across the whole chip. The fact that excessive etching can be experimentally suppressed by negative bias further supports the assumption that the excessive etching is caused by excessive h<sup>+</sup>.

To further illustrate the proposed mechanism of EMaCE, we replaced the constant bias by a variable bias that continuously increased from -0.10 to -3.10 V at 5 mV/s (referred as continuous EMaCE experiment). The current-bias (I-V) curve of the continuous EMaCE experiment is shown as the black line in Figure 5a. The sign of current is defined as negative, meaning that h<sup>+</sup> is flowing away from the chip and electrons are injected into the chip. Because the Si substrate is *p*-type, the contact between the back side of Si and the copper foil can be treated as a forward-biased Schottky contact. The nonlinear increase of current versus bias beyond the onset of ca. -0.6 V is characteristic for forward-biased Schottky contact. After the bias exceeds -1.5 V, the evolution of current became unstable, which may be due to the slow depletion of excessive h<sup>+</sup>. In contrast, when the same experiment was done in a  $\rho(1)^{1.8}$

etchant (i.e., etchant without  $H_2O_2$ ), the current stays negligibly low across the whole etching experiment (red line, Figure 5a). Actually, Au catalysts hardly etched into the substrate in  $\rho(1)^{1.8}$ , and only some pores (<100 nm diameter) propagated along the family of  $\langle 100 \rangle$  crystalline orientation around the Au (Figure S6, Supporting Information). The control experiment indicates that catalyzed reduction of  $H_2O_2$ is the source of the current in EMaCE (black line Figure 4a), and the charge carriers of the current mainly consist of excessive h<sup>+</sup>. Thus, EMaCE is essentially different from traditional electrochemical etching<sup>28</sup> in which  $h^+$  is injected from an external power supply. We also plot the value of  $\tan\theta$ from Figure 4c-f against the bias as blue dots in Figure 5a, which shows a decreasing trend similar to that of current. Because tan  $\theta$  approximately equals to  $2h/(d_t - d_b)$ , tan  $\theta$  can roughly represent the ratio of the vertical etching rate to the excessive etching rate. The similarity between the trends of I-Vand  $tan(\theta - V)$  indicates that the extent of excessive etching suppression can be related to the amount of h<sup>+</sup> that are drawn to the back side. Further, we did an EMaCE experiment where the applied bias varied versus etching time in a stepwise manner (referred to as stepwise EMaCE). The evolution of applied bias and measured current versus the etching time are shown in Figure 5b. The etching process can be divided into four stages. In each stage, the bias stayed at a constant value for 300 s. The transition time of the bias and current between two stages are both less than 1 s. The current changed and stabilized itself after the bias was altered to a new value with delay time less than 1 s. The slight increase of current in each stage may be caused by the geometric evolution of the etching profile. The etching result of continuous EMaCE and stepwise EMaCE are shown in Figure 5c-e and f-h, respectively. In continuous EMaCE, the sidewall angle increased as the Au etched deeper; the sidewall angle become 90° around 20  $\mu$ m below the top surface. In stepwise EMaCE, the sidewall angle increased stepwise. In both cases, some discontinuity on the smooth sidewall can be observed (Figure 5d,f, insets). These sharp turns show the geometric response of etching profile to the attenuation of applied bias.<sup>29,30</sup> Also, the etching profiles are uniform across the whole chips, as illustrated by the lowmagnification SEM images of polymer replica (Figure 5e,h). The success of continuous EMaCE and stepwise EMaCE demonstrates that both the lateral and the vertical geometry of the etching profile can be controlled in a real-time manner by the facile attenuation of bias over etching time.

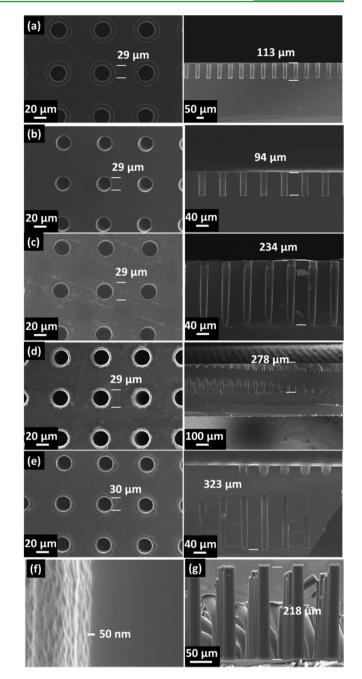

To investigate capability of high-speed etching by EMaCE, we performed EMaCE in  $\rho(0.55)^{3.6}$  etchant. After 10 min of etching, the catalysts penetrated 113  $\mu$ m into the silicon substrate with a sidewall angle >89° (Figure 6a,b). When viewed under SEM with high magnification, the sidewall shows a roughness well below 50 nm (Figure 6f). The low sidewall roughness (<50 nm) at high etching speed (>10  $\mu$ m/min) makes the etched holes ideal candidates for high performance through silicon vias. In contrast, in dry etching, the sidewall roughness is usually compromised at an etching rate higher than 5  $\mu$ m/min.<sup>24</sup> Further increasing the  $\rho$  value of the etchant may cause the catalysts to break. As shown in Figure S7 (Supporting Information), after etching in  $\rho(0.65)^{5.2}$  at -1.75V for 10 min, Au catalysts broke into separate particles. Randomly aligned pores were formed on both the top surface and the bottom of the etched holes (Figure S7a,b, Supporting Information), because a porous silicon-formation h<sup>+</sup> transport was enabled in the high- $\rho$  etchant.<sup>23</sup> Further, we investigated

Research Article

**Figure 6.** (Left) Top-view and (right) cross-sectional of the chips etched at -1.75 V for (a) 10 min in  $\rho(0.37)^{1.8}$ , (b) 25, (c) 60, (d) 90, and (e) 120 min. (f) Sidewall of etched holes in panel a with high magnification. (g) Polymer replica of chip in panel d.

the capability of EMaCE in etching structures with high aspect ratio. Figure 6b–d shows the chips after EMaCE in  $\rho(0.37)^{1.8}$ at -1.75 V for 25 min, 60 min, 90 and 120 min. In each test, the etchant was agitated by a stir bar at 400 rpm after 10 min of EMaCE;  $d_t$  remained 29  $\mu$ m in each test; and h was measured each time from cross sections of the etched chips, which are 94, 235, 278, and 323  $\mu$ m, respectively. The low-magnification images of the chips after 25 min of etching show good uniformity across the whole chips (Figure S8a,b, Supporting Information). After an etching time of 120 min, the vertical etching direction was still preferred. The Au catalyst maintained its integrity without breaking, and the sidewall roughness remained as low as that shown in Figure 6f. We also tried to use

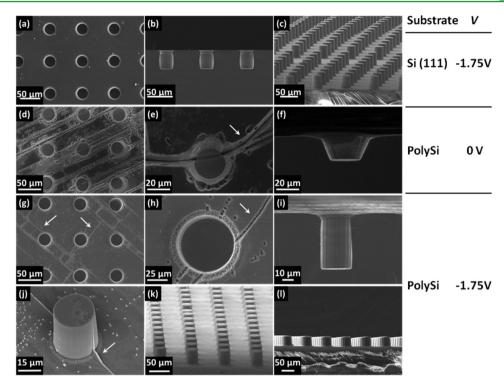

**Figure 7.** (a) Top-view and (b) cross-sectional SEM images of a 29  $\mu$ m Au–Si(111) chip after MaCE at -1.75 V and (c) corresponding replica. (d and e) Top-view and (f) cross-sectional SEM images of a 29  $\mu$ m Au-polySi chip after MaCE. (g and h) Top-view and (i) cross-sectional SEM images of a 29  $\mu$ m Au-polySi chip after MaCE at -1.75 V. (j–l) Corresponding replicas.

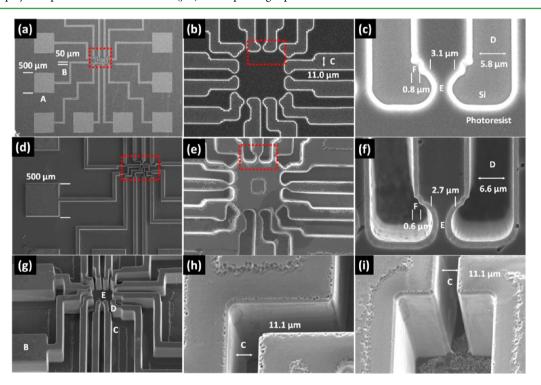

Figure 8. (a–c) Pattern of a complex feature after photolithography on Si(100) chip; (e–h) the chip after EMaCE at -2.00 V for 10 min; and (d and g) the corresponding replicas.

polymer replica to reveal the 3D geometry of these high-aspectratio structures. However, because of the limited mechanical property of epoxy replica, only straight polymer replica with the height of 218  $\mu$ m was found. Some replica with a height of 270  $\mu$ m can also be found while tilting from the vertical direction (Figure S8c, Supporting Information). It should be noted that after etching for 120 min at -1.75 V, the photoresist stayed in close contact with the top surface of silicon substrate (Figure S8d, Supporting Information). In contrast, the top surface was significantly etched, and a gap appeared after 20 min of MaCE at no bias (Figure S8e, Supporting Information) and finally caused the delaminating of photoresist. The results shown in

Figure 6b–e demonstrate that EMaCE is capable of producing microstructures deeper than 300  $\mu$ m with an aspect ratio greater than 10:1 while completely suppresses the excessive etching over the etching long time.

To extend the range of application, we applied the established EMaCE method to the BMS of (111)-oriented Si substrate and polycrystalline Si (polySi) substrate. Figure 7a-c shows the top-view and cross-sectional SEM images of a 29  $\mu$ m Au-Si(111) chip after EMaCE for 10 min at -1.75 V and the corresponding replica. Uniform vertical holes can be found across the whole chip. For polySi substrate, we first studied the etching behavior at no bias (Figure 7d-f). After etching for 10 min, Au catalysts moved vertically into the substrate. However, a considerable amount of grooves and pits were found on the Si between Au (Figure 7d). It has long been known that chemical etching of Si is preferable along the defects of Si substrates.<sup>31</sup>Thus, the grooves were probably formed by the excessive etching of the boundary between two adjacent Si crystal grains. At higher magnification, some grooves were found to penetrate below the Au catalysts, indicating that the excessive etching of grain boundary even exceeded the MaCE process (indicated by the white arrow Figure 7e). Also, the sidewall of the etched holes tapered like those shown in Figure 2. In contrast, when a -1.75 V bias was applied, both the groove formation and sidewall tapering were suppressed (Figure 7g-i). Although some shallow grooves were still observable, the grooves only penetrated into the very top layer of Si substrates, as revealed from the etched chip (Figure 7h) and its corresponding replica (Figure 7j). Also, etching in the vertical direction was significantly enhanced by the bias (Figure 7i) compared to that at not bias (Figure 7f). The SEM of polymer replica in low magnification (Figure 7k,l) shows that the vertical etching was preferred across the chip, and all the etched holes bear high geometric uniformity. The crystalline orientation-independent etching behavior is highly desirable for BMS on broader range of substrates.

Finally, we tested the BMS of complex features by EMaCE. Figure 8a-c shows the original pattern of a complex feature after photolithography. Five sets of subunits with critical dimensions of (A) 500, (B) 50, (C) 11.7, (D) 5.8, (E) 3.1, and (F) 0.8  $\mu$ m can be observed in the images with increasing magnification (Figure 8). We increased the bias to -2.00 V because a larger amount of excessive h<sup>+</sup> was produced by the larger area of Au catalysts. After 10 min of EMaCE, Au catalysts on all units etched uniformly and vertically into the Si substrate, as shown in the polymer replica (Figure 8d,g). The values of  $d_t$ and  $d_{\rm b}$  were measured from the etched chips (Figure 8e,f) and corresponding polymer replica (Figure 8g), respectively. The values are listed in Table 1. The variance between  $d_{\rm t}$  and  $d_{\rm b}$  of each subunit is less than 1  $\mu$ m, both of which have a variance less than 1  $\mu$ m to their origin dimensions ( $d_{\text{orig}}$ ). Besides the accuracy of dimensions, EMaCE also possesses the fidelity in transferring the shape of original features, as found in the sharp

Table 1. Dimensions of Subunits C–F Shown in Figure 8 before and after EMaCE

| feature ID                 | С    | D   | Е   | F   |

|----------------------------|------|-----|-----|-----|

| $d_{\rm orig}(\mu { m m})$ | 11.0 | 5.8 | 3.1 | 0.8 |

| $d_{\rm t}(\mu{\rm m})$    | 11.1 | 6.6 | 2.7 | 0.6 |

| $d_{\rm b}(\mu{ m m})$     | 10.2 | 5.0 | 2.7 | 0.8 |

corners (Figure 8h) and interconnections between features B and C (Figure 8i).

# CONCLUSION

In conclusion, a novel silicon etching method, named electric bias-attenuated metal-assisted chemical etching (EMaCE), is established on the basis of the uniform MaCE condition. A negative electric bias was applied from the back side of Si substrate during MaCE process to solve the issue of excessive etching found in traditional MaCE process. Over 10 000 vertical holes with diameter of 28  $\mu$ m were successfully fabricated on a 1 cm<sup>2</sup> chips with high speed, high aspect ratio, and low sidewall roughness. By programming the variation of bias versus etching time, the 3D geometry of the etching profile can be attenuated in real time. Etching of vertical holes was also realized by EMaCE on Si (111) and polySi substrate. Complex features with lateral dimensions of 0.8  $\mu$ m-500  $\mu$ m were also fabricated with high geometric accuracy. The established EMaCE is not only readily applicable for manufacturing TSVs in large scale with low cost, but it is also available for MEMS devices with complex lateral geometry. Also, EMaCE provides a viable solution for direct deep etching of polycrystalline silicon, which has been challenging so far. Further, EMaCE with variable bias is promising to create novel micro- and nanostructures with arbitrarily defined 3D complexity that spur the leap in microelectronics packaging, MEMS, photonic devices, and so on.

#### EXPERIMENTAL SECTION

Substrate Preparation. Boron-doped (100)-, (111)-oriented single crystalline silicon wafers (1–10  $\Omega$ ·cm) and polycrystalline silicon wafers (boron-doped, 1–10  $\Omega$ ·cm) with one side polished were purchased from University Wafer (Boston, MA). In a Class 10 cleanroom, the wafers were cleaned in Piranha solution (1:3 volume ratio of H<sub>2</sub>O<sub>2</sub> (30 wt %) and H<sub>2</sub>SO<sub>4</sub> (96 wt %))at 120 °C for 10 min, and then dipped in 1% w/w aqueous HF solution to remove the oxide layer. The cleaned wafers were dried in N2. For photolithography, a 1.6  $\mu$ m-thick layer of negative photoresist NR9–1500PY (Futurrex, Inc., Franklin, NJ) was spin cast on the front (polished) side of the cleaned wafer and exposed in a mask aligner (Karl Suss MA6) by 365 nm UV light with a dosage of 190 mJ/cm<sup>2</sup>. The exposed wafer was developed by immersion in Resist Developer RD6 (Futurrex, Inc., Franklin, NJ). All the wafers with patterned resist are treated with oxygen plasma (RF power: 22 W) in an RIE tool (Plasma Therm, Inc.) to remove any polymer residue on exposed areas and make the silicon surface terminated by oxygen (Si-O). Au catalysts were deposited on the front side by an electron beam evaporator at a rate of 0.5 Å/s in a vacuum atmosphere of  $3 \times 10^{-6}$  Torr (CVC Product, Inc.). Then, 10 nm thick titanium and 200 nm thick copper were deposited on the back side of the wafers using the same method. In this report, the thickness refers to the nominal value measured by an in situ monitor (Maxtek Sensor Crystal Gold 6 MHz 74016-1139 P/N 103220, Inficon), unless specified.

**Etching and Characterization.** The wafers were cut into 1 cm<sup>2</sup> chips and mounted on homemade carriers before etching. Briefly, the carriers were made by spreading a layer of copper foil (0.127 mm thick, Alfa Aesar) on a  $1.5 \times 2.0$  cm glass slide. A polymer-coated copper wire (0.50 mm conductor diameter, R24BLK-0100, OK Industries) was soldered on one corner of the copper foil. The edge of the carrier was sealed by epoxy precursor and cured at 150 °C for 1 h in an atmospheric oven. The epoxy precursor was prepared by mixing 17 g of EPON Resin 862, (Hexion Special Chemicals, Inc.), 20 g of Lindride 52D (Lindau Chemicals) and one drop of 2-ethyl-4-methyl-1*H*-Imidazole-1-propanenitrile (Aldrich) as catalyst. After sealed in the epoxy, the chip was mounted on the copper foil, which had been wetted by liquid gallium for good electric contact. The test vehicle was

further sealed by polyimide tape to make only the front sides of chips exposed (Figure S3, Supporting Information). To prepare the etchant, HF (48-52 wt % in H<sub>2</sub>O), H<sub>2</sub>O<sub>2</sub> (30 wt % in H<sub>2</sub>O, Anachemia Chemicals, LLC) and deionized water (DI water, resistivity ~18.2  $M\Omega$ ) were directly mixed without further processing. DI water was produced by a Thermo Scientific Barnstead Smart2Pure water purification system. The total volume of the etchant was fixed to 32 mL. The etching was conducted by gently immersing the test vehicle in the etchant solution in a loosely capped transparent polyethylene (PE) tube (VWR International, Suwanee, GA) for a certain amount of time. The PE tube with etchant was preheated in a silicone oil bath with controlled temperature on a hot plate (VWR International, Radnor, PA) for 20 min before etching and kept immersed in the bath until etching was finished. After being etched, the chips were taken off the carriers and cleaned by Piranha solution described above. Note: HF-H<sub>2</sub>O<sub>2</sub> mixture and Piranha solution is highly corrosive, thus the etching and cleaning were done in a well-ventilated fume hood with proper personal protection equipment. A constant bias was generated by a power supply (Farnell PSD 3510A). The variable voltage was produced and recorded by a potentiostat (Princeton Applied Research, VersaSTAT MC). The bias was applied 30 s after the chip was immersed in the etchant to stabilize the Au catalysts. The polymer replica was fabricated by dipping the epoxy precursor on the front side of cleaned chips after etching and cured at 150 °C in a vacuum oven for 1 h. The replica is isolated by completely removal of silicon in the mixture of HNO<sub>3</sub> (70 wt %) and HF (49 wt %) with the volume ratio of 1:6 within 10 min at room temperature. The polymer replica was coated by Au (less than 20 nm thick) for SEM imaging in a DCsputter (Denton DeskII). SEM images were taken from Zeiss LEO 1550 thermally assisted field emission (TFE) SEM or Hitachi SU8010 SEM operating at 10 keV with a working distance between 2 and 7 mm. Optical confocal microscope image and cross sections were obtained from Olympus LEXT OLS4000 laser confocal microscope. The depth of pre-etching step was measured by Tencor P15 Profilometer using stylus. Matlab 7.0 software was used for modeling h<sup>+</sup> concentration.

#### ASSOCIATED CONTENT

#### **Supporting Information**

SEM images and details of h+ simulation. This material is available free of charge via the Internet at http://pubs.acs.org.

#### AUTHOR INFORMATION

Corresponding Author

\*E-mail: cpwong@cuhk.edu.hk.

# Author Contributions

L.L. conducted the experiments and analyzed the data. X.Z. did the simulation of  $h^+$  concentration. The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The authors thank the funding support from the Nation Science Foundation (CMMI #1130876). The authors appreciate the helpful discussion from Dr. Ziyin Lin, Dr. Kyoung-Sik Moon, Mr. Devin Brown, and all the staff at the Institute for Electronics and Nanotechnology at Georgia Tech.

# REFERENCES

(1) Motoyoshi, M. Through-Silicon Via (TSV). Proc. IEEE 2009, 97, 43–48.

(2) Ayazi, F.; Najafi, K. High Aspect-Ratio Combined Poly and Single-Crystal Silicon (HARPSS) MEMS Technology. J. Microelectromech. Syst. 2000, 9, 288–294. (3) Bruccoleri, A.; Guan, D.; Mukherjee, P.; Heilmann, R. K.; Schattenburg, M. L.; Vargo, S. Potassium Hydroxide Polishing of Nanoscale Deep Reactive-Ion Etched Ultrahigh Aspect Ratio Gratings. *J. Vac. Sci. Technol. B* **2013**, 31.

(4) Pal, P.; Sato, K. Various Shapes of Silicon Freestanding Microfluidic Channels and Microstructures in One-Step Lithography. J. Micromech. Microeng. 2009, 19.

(5) King, C. R.; Sekar, D.; Bakir, M. S.; Dang, B.; Pikarsky, J.; Meindl, J. D. 3D Stacking of Chips with Electrical and Microfluidic I/O Interconnects, In Proceedings of the Electronic Components and Technology Conference, 2008. IEEE 58th, Orlando, Florida, May 27–30, 2008; pp 1–7.

(6) Chang, C.; Wang, Y.-F.; Kanamori, Y.; Shih, J.-J.; Kawai, Y.; Lee, C.-K.; Wu, K.-C.; Esashi, M. Etching Submicrometer Trenches by Using the Bosch Process and Its Application to the Fabrication of Antireflection Structures. J. Micromech. Microeng. 2005, 15, 580–585. (7) Wang, X. D.; Zeng, W. X.; Eisenbraun, E. Sub-0.25 Micron Silicon Via Etching for 3D Interconnects. J. Micromech. Microeng. 2007, 17, 804–811.

(8) Robbins, H.; Schwartz, B. Chemical Etching of Silicon 0.1. The System HF, HNO<sub>3</sub>, and H<sub>2</sub>O. J. Electrochem. Soc. 1959, 106, 505-508.

(9) Turner, D. R. Electropolishing Silicon in Hydrofluoric Acid Solutions. J. Electrochem. Soc. 1958, 105, 402-408.

(10) Lehmann, V.; Föll, H. Formation Mechanism and Properties of Electrochemically Etched Trenches in *n*-Type Silicon. *J. Electrochem.* Soc. **1990**, 137, 653–659.

(11) Williams, K. R.; Muller, R. S. Etch Rates for Micromachining Processing. J. Microelectromech. Syst. 1996, 5, 256–269.

(12) Huang, Z.; Geyer, N.; Werner, P.; de Boor, J.; Gösele, U. Metal-Assisted Chemical Etching of Silicon: A Review. *Adv. Mater.* 2011, *23*, 285–308.

(13) Li, X.; Bohn, P. W. Metal-Assisted Chemical Etching in HF/  $H_2O_2$  Produces Porous Silicon. *Appl. Phys. Lett.* **2000**, 77, 2572–2574.

(14) Chartier, C.; Bastide, S.; Lévy-Clément, C. Metal-Assisted Chemical Etching of Silicon in HF–H<sub>2</sub>O<sub>2</sub>. *Electrochim. Acta* **2008**, *53*, 5509–5516.

(15) Chen, C.-Y.; Wu, C.-S.; Chou, C.-J.; Yen, T.-J. Morphological Control of Single-Crystalline Silicon Nanowire Arrays Near Room Temperature. *Adv. Mater.* **2008**, *20*, 3811–3815.

(16) Chen, C.-Y.; Li, L.; Wong, C.-P. Evolution of Etching Kinetics and Directional Transition of Nanowires Formed on Pyramidal Microtextures. *Chem.-Asian J.* 2014, *9*, 93–99.

(17) Li, L.; Wong, C. P. High Aspect Ratio Sub-100 nm Silicon Vias (SVs) by Metal-Assisted Chemical Etching (MaCE) and Copper Filling, In Proceedings of the Electronic Components and Technology Conference (ECTC), 2013. IEEE 63rd, Las Vegas, Neveda, May 28–31, 2013; pp 2326–2331.

(18) Huang, Z.; Zhang, X.; Reiche, M.; Liu, L.; Lee, W.; Shimizu, T.; Senz, S.; Gösele, U. Extended Arrays of Vertically Aligned Sub-10 nm Diameter [100] Si Nanowires by Metal-Assisted Chemical Etching. *Nano Lett.* **2008**, *8*, 3046–3051.

(19) Huang, Z.; Shimizu, T.; Senz, S.; Zhang, Z.; Zhang, X.; Lee, W.; Geyer, N.; Gösele, U. Ordered Arrays of Vertically Aligned [110] Silicon Nanowires by Suppressing the Crystallographically Preferred (100) Etching Directions. *Nano Lett.* **2009**, *9*, 2519–2525.

(20) Kim, J.; Kim, Y. H.; Choi, S.-H.; Lee, W. Curved Silicon Nanowires with Ribbon-like Cross Sections by Metal-Assisted Chemical Etching. ACS Nano 2011, 5, 5242–5248.

(21) Chang, S. W.; Chuang, V. P.; Boles, S. T.; Thompson, C. V. Metal-Catalyzed Etching of Vertically Aligned Polysilicon and Amorphous Silicon Nanowire Arrays by Etching Direction Confinement. *Adv. Funct. Mater.* **2010**, *20*, 4364–4370.

(22) Güder, F.; Yang, Y.; Küçükbayrak, U. M.; Zacharias, M. Tracing the Migration History of Metal Catalysts in Metal-Assisted Chemically Etched Silicon. *ACS Nano* **2013**, *7*, 1583–1590.

(23) Li, L.; Liu, Y.; Zhao, X.; Lin, Z.; Wong, C.-P. Uniform Vertical Trench Etching on Silicon with High Aspect Ratio by Metal-Assisted Chemical Etching Using Nanoporous Catalysts. *ACS Appl. Mater. Interfaces* **2014**, *6*, 575–584.

(24) Hsin, Y.-C.; Chen, C.-C.; Lau, J. H.; Tzeng, P.-J.; Shen, S.-H.; Hsu, Y.-F.; Chen, S.-C.; Wn, C.-Y.; Chen, J.-C.; Ku, T.-K.; Kao, M.-J. Effects of Etch Rate on Scallop of Through-Silicon Vias (TSVs) in 200 mm and 300 mm Wafers. In Proceedings of the Electronic Components and Technology Conference (ECTC), 2011. IEEE 61st, Orlando, Florida, May 31–June 3, 2011; pp 1130–1135.

(25) Gondek, C.; Lippold, M.; Rover, I.; Bohmhammel, K.; Kroke, E. Etching Silicon with HF-H<sub>2</sub>O<sub>2</sub>-Based Mixtures: Reactivity Studies and Surface Investigations. *J. Phys. Chem. C* 2014, *118*, 2044–2051.

(26) Cheng, S. L.; Chung, C. H.; Lee, H. C. A Study of the Synthesis, Characterization, and Kinetics of Vertical Silicon Nanowire Arrays on (001)Si Substrates. J. Electrochem. Soc. **2008**, 155, D711–D714.

(27) Lianto, P.; Yu, S.; Wu, J.; Thompson, C. V.; Choi, W. K. Vertical Etching with Isolated Catalysts in Metal-Assisted Chemical Etching of Silicon. *Nanoscale* **2012**, *4*, 7532–7539.

(28) Lehmann, V.; Gosele, U. Porous Silicon Formation: A Quantum Wire Effect. *Appl. Phys. Lett.* **1991**, *58*, 856–858.

(29) Kim, J.; Rhu, H.; Lee, W. A Continuous Process for Si Nanowires with Prescribed Lengths. J. Mater. Chem. 2011, 21, 15889–15894.

(30) Huang, Z. P.; Geyer, N.; Liu, L. F.; Li, M. Y.; Zhong, P. Metal-Assisted Electrochemical Etching of Silicon. *Nanotechnology* **2010**, *21*, 465301.

(31) Zhang, X. G. Electrochemistry of Silicon and Its Oxide; Kluwer Academic/Plenum Publishers: New York, 2001; p 338.